LAPORAN

HASIL PRAKTIKUM PART 4

(COUNTER)

1.

Tujuan

Praktikum

Kegiatan

pembelajaran ini bertujuan agar mahasiswa mendapat kesempatan untuk menguji,

dan mengaplikasikan teori atau penyelidikan dan pembuktian pada perkuliahan

blok yang sedang di ampu. Praktikum yang kami lakukan pada blok Dasar Teknologi

Informasi ini di ampu oleh beliau Ibu, Adelia Octora P.S. Si., M. T. , dan di

lakukan di rumah masing masing karena masih pembelajaran secara daring.

Praktikum yang kami lakukan kali ini juga bukan praktikum yang pertama, melainkan

praktikum ke-4. Namun pada praktek kali ini kita menguji rangkaian flip flop

counter. Untuk langkah dan cara kerja bisa kita simak pada laporan di bawah

ini.

2. Alat dan Bahan

Alat

dan bahan yang di butuhkan anatara lain :

· Laptop/PC

· Internet/Jaringan

· Komponen

7SEG-MPX1-CA

· Gate

7447

· Gate

7473

· CLOCK

· LogicState

· MINRES100R

· SW-SPST

Selain

itu kita perlu komponen tambahan yang berada di terminal mode di antaranya :

· Power

· Ground

3. Langkah Kerja

a.

Simulasi

menggunakan satu Clock dan dua LogicStateclock

1. Letakkan

gate 7SEG-MPX1-CA (Tarik menuju halaman utama)

2. Letakkan

satu gate 7447

3. Letakkan

4 gate 7473

4. Input

1 clock

5. Serta

2 logicstate

CARA KERJANYA

1. Jumlah

minres yang kita ambil ada 8

2. 7

diantaranya diletakkan di sebelah kanan gate 7447

3. Sedangkan

yang satu diletakkan di bawah MPX dekat

kaki bawah sebelah kanan

4. Letakkan

SW-SPST di sebelah kanan minres ke delapan

5. Power

di letakkan di dekat MPX

6. Ground

di letakkan di bawah SW-SPST

7. Letakkan

clock di tengan antara dua logicstate

8. Logicstate

yang kedua(bagian bawah), di sambungkan ke gate 7473 bagian akhir (U23) di kaki

R

9. Setiap

gate 7473, pada kaki R di sambungkan pula ke kabel pertama (kabel no 8)

10. Setiap

pada gate 7473, kaki J & K di sambungkan dengan satu kabel

11. LogicState

ke 1 di sambungkan ke kaki 1 pada gate 7473 pertama,begitupun dengan clock

12. Clock

di sambungkan ke kaki clock pada gate 7473 pertama

13. Kaki

Q pada setiap gate 7473 di sambungkan kabel menuju output pada gate 7473 di

depannya, namun sambungkan dengan clock.

14. Setiap

kaki J & K di hubungkan / dengan satu kabel pada setiap gate 7473

15. Kaki

pada MPX itu ada 9, 7 di antaranya, di sambungkan ke kaki minres yang terletak di sebelah kanan

16. Kaki

ke 8 MPX di sambungkan pada minres ke 8

17. Sedangkan

kaki terakhir/kaki ke 9 di sambugkan ke power

18. Minres

ke 8 juga di sambungkan ke SW-SPST

19. Dilanjutkan

SW-SPST disambungkan ke ground

20. Semua

kaki minres yang terletak di sebelah kiri, di sambungkan dengan kaki pada gate

7447 bagian kanan

21. Kaki

A pada gate 7447 disambungkan ke output Q yang pertama di gate 7473 pertama

22. Kaki

B pada gate 7447 disambungkan ke output Q di gate 7473 ke dua

23. Kaki

C pada gate 7447 disambungkan ke output Q di gate 7473 ke tiga

24. Kaki

D pada gate 7447 disambungkan ke output Q di gate 7473 ke empat

SIMULASIKAN

· Jika

inputan yang di masukkan pada logicState adalah 1 dan 1 maka keluaran akan

berjalan

· Sedangkan

jika inputan yang di masukkan adalah (1,0), (0,1), (0,0), maka keluaran akan

tetap 0 / tidak berjalan

b.

Simulasi

menggunakan 3 LogicStateclock

Untuk simulasi menggunakan 3 LogicState

hanya perlu mengubah masukan clock pada rangkaian sebelumnya menjadi

logicstate. Sehingga inputan yang di masukkan adalah 3 logicstate. Tidak ada

rangkaian atau kabel yang perlu di ubah hanya saja akan berbeda pada

simulasinya.

SIMULASIKAN

· Jika

inputan yang di masukkan adalah (1,0,1), maka keluaran akan muncul

· Sedangkan

jika masukkannya adalah (1,1,1), (1,0,0), (1,1,0), (0,1,1),

(0,0,0), (0,0,1), dan (0,1,0), maka keluaran

akan mati (tidak berjalan.

PEMBAHASAN

1.

GAMBAR

1

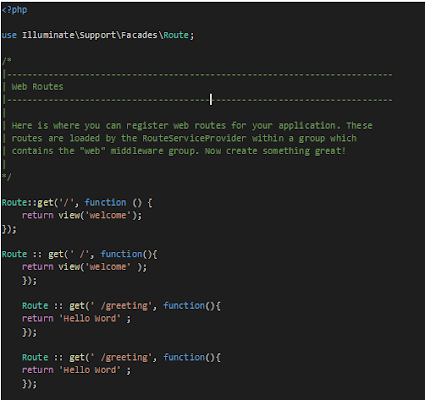

Gambar 1 merupakan gambar simulasi yang pertama. Yang mana

pada gambar tersebut menggunakan inputan dua logic state dan satu clock. Logicstate

yang akan disimulasikan harus menginputkan inputan 1, karena jika bukan 1 maka

keluaran tidak akan berjalan.

2. GAMBAR

2

Gambar 2 merupakan gambar pada simulasi yang ke dua. Yang

mana pada gambar tersebut menggunakan inputan tiga logicstate. Inputan pada

logicstate yang dimasukkan merupakan (1,0,1). Jika nilai yang di inputkan bukan

itu, maka keluaran tidak akan berjalan.

Simulasi simulasi yang di lakukan di atas merupakan simulasi counter menggunakan aplikasi proteus. Teman teman juga bisa melakukan simulasi menggunakan aplikasi lain. Step by step sudah tertera di atas, tinggal kita terapkan saja. Jika masih ada yang kurang bisa di pahami bisa tulis di kolom komentar. Semoga bermanfaat, salam semangat dan TERIMAKASIH.

.png)

.jpg)

.png)

.png)